AHB_Lite 通信协议的FPGA Verilog 设计

”ahb_fpga ahb-lite__verilog ahb ahb协议 verilog设计ahb“ 的搜索结果

AMBA_3_AHB-Lite协议中文版

AHB-Lite接口转换模块完整Verilog代码以及测试文件

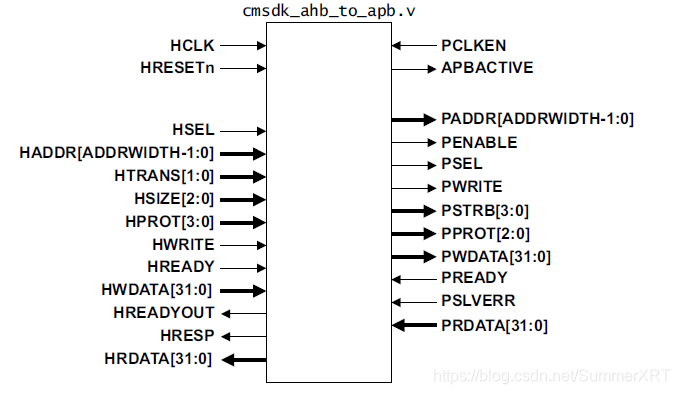

AMBA中的AHB总线是我们经常...本文主要实现了一个基础的将模块内部简单的读写信号转换为AHB-Lite协议信号的转换模块。提示:未经授权,严禁转载。模块框图中左边的信号是内部信号,右边是转换后得到的AHB-Lite信号。

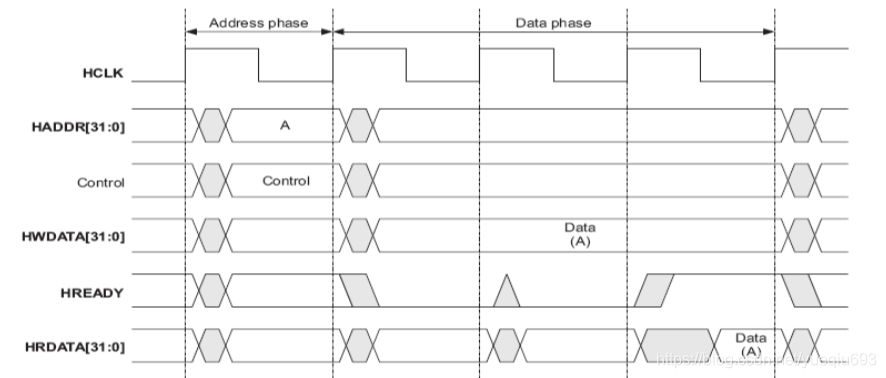

AHB-lite时序详细解读

标签: arm

本文讨论了SoC系统的架构设计,包括处理器核心、内存以及其他外设的互连,并详细描述了如何通过AHB-Lite总线实现高效的数据传输。AHB-Lite总线是一种简化版本的AHB总线。同时,阐述了利用寄存器映射以及其他硬件资源...

AHB_Lite和APB总线入门 1. 概述 AHB总线(the Advanced High-performance Bus)和APB总线(the Advanced Peripheral Bus)由ARM公司研发的AMBA(Advanced ...在一些非常简单的系统中,主要使用的是AHB-Lite总线(以下

AHB-Lite是ARM公司提出的一种高级总线...总之,AHB-Lite主从连接在Verilog中的实现是一个复杂的过程,需要对AHB-Lite协议规范有详细的了解,同时需要有Verilog语言的熟练掌握,才能完成一个可靠的AHB-Lite总线连接。

设计了一个AHB从机接口模块,提供AHB总线到从机Memory的接口

AHB3-lite 互连:负责在 AHB3-lite 协议中允许主从之间通信的互连 模式检测器:实现一个简单状态机的核心,当在其输入总线上看到模式“f0f0f0f0”时切换其输出 当板子打开时,cortex-m0 读取 RAM 内存,该内存是用一...

基于AMBA总线描述了一个AHB接口,采用多主多从的架构,有多个master和slave

AHB_SLAVE(SD_IF)部分代码如下: module sd_if ( //-- ahb input hclk; input hrst_n; input hsl; input hwrite;//1->write 0->read input [1:0] htrans; //4种 idel busy seq nons...

一、AHB总线学习 1. AHB总线结构 如图所示,AHB总线系统利用中央多路选择机制实现主机与从机的互联问题。从图中可以看出,AHB总线结构主要可分为三部分:主机、从机、控制部分。控制部分由仲裁器、数据多路选择...

在Verilog HDL中,实现一个AHB Lite接口需要注意以下几点: 首先,在模块的接口定义上,应该包含AHB Lite总线的标准信号定义,例如AHB Lite总线时钟、AHB Lite总线重置、读写使能和传输控制等等,这些信号都是必不...

设计AHB2APB同步桥

标签: 芯片

在SOC的搭建过程中,CPU通过AMBA规范的AHB-lite总线通过控制模块和外部设备进行数据的交互,这里用Verilog描述了一个串口,实现了CPU和外部设备的数据交换和通信。

在SOC的搭建过程中,CPU通过AMBA规范的AHB-lite总线通过控制模块和外部设备进行数据的交互,这里用Verilog描述了一个串口,实现了CPU和外部设备的数据交换和通信。

推荐文章

- python入门(13)异常与文件_except filenotfounderror:-程序员宅基地

- Android面试攻略_详细了解在当今的社会里android工程师应具备什么的技能?并能详细说说自己的见解。-程序员宅基地

- Zendframework 1.6整合Smarty_setting private or protected class member is not a-程序员宅基地

- Qt-装饰者模式_qt装饰模式-程序员宅基地

- 新开普掌上校园服务管理平台service.action RCE漏洞复现 [附POC]-程序员宅基地

- 基于 Milvus 的音频检索系统-程序员宅基地

- 331、基于51单片机智能红外遥控暖风机温度无线蓝牙远程控制系统设计(程序+原理图+配套资料等)_红外感应暖风机自动控制系统设计-程序员宅基地

- Android自定义圆角矩形图片ImageView_android 矩形圆角imageview-程序员宅基地

- 又见回文 字符串-程序员宅基地

- switch的参数可以是什么类型?_switch的参数有哪些-程序员宅基地